存储器

概述

一、 存储器分类

按存储介质分类

半导体存储器 (易失)

- TTL (晶体管、晶体管、逻辑) :集成度低,功耗高,速度快

- MOS(金属、氧化物、半导体) : 功耗低,集成度高,构成现代计算机存储器(尤其是内存)

- 磁表面存储器(磁盘、磁带)

磁头、磁载体 - 磁芯存储器 (王安博士 1948年)core memory

硬磁材料,环状元件 - 光盘存储器

按存取方式分类

存取时间与物理地址无关(随机访问)

- 随机存储器 (RAM)

在程序执行过程中可读可写 - 只读存储器

在程序执行过程中只读,存放系统参数或系统程序。

- 随机存储器 (RAM)

存取时间与物理地址有关(串行访问)

- 顺序存储存储器:磁带

- 直接存取存储器: 磁盘

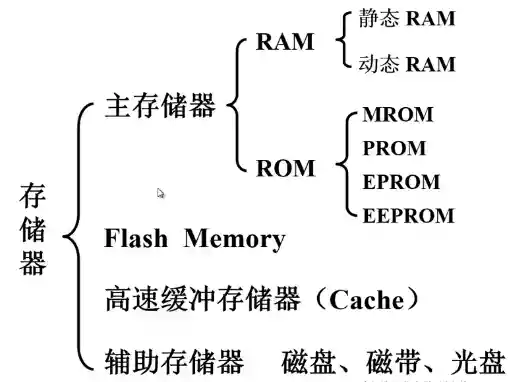

按在计算机中的作用分类:

主存储器:

RAM (随机访问存储器)

- 静态RAM

- 动态RAM

ROM (只读存储器)

- MROM: 掩膜型只读存储器

- PROM:可编程只读存储器

- EPROM:电可编程只读存储器

- EEPROM:电可擦写可编程只读存储器

- Flash Memory:一种半导体存储器,速度比磁盘快,比主存储器慢

- 告诉缓冲存储器(Cache):存在于主存储器和CPU之间

- 辅助存储器: 磁盘、磁带、光盘

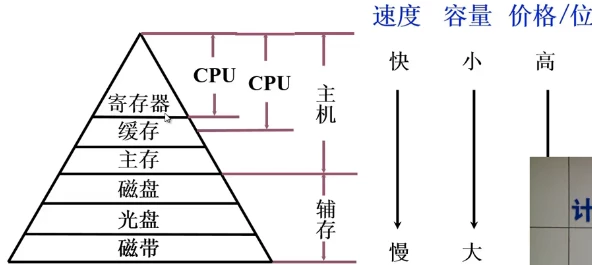

二、 存储器的层次结构

存储器三个主要特性的关系

容量 速度 价位

在此金字塔形的存储器层次结构中速度、容量、价位由上到下依次是:

速度由快到慢

容量由小到大

价格由高到低- 为什么要整这么多种类?

-满足用户的需求,用户需求高速大容量低价格。因此要使用多种存储器构成一个存储体系。 - 存储体系:用两种及以上存储介质构成的存储器,用软硬件将它们连接成一个整体,使得对于某一级程序员来说可以得到一个理想的储存器。

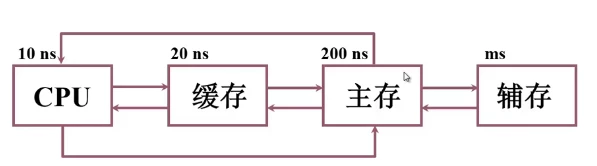

两个重要的存储层次

缓存-主存层次

主存-辅存层次

对于应用程序员来说,这个整体拥有主存的速度,辅存的容量和价格。程序数据的调度由‘软硬件’实现。

- 缓存-主存层次:这个层次主要解决速度问题,使用主存储器的地址——实地址(物理地址)。

- 主存-辅存层次:主要解决,容量问题,又称虚拟存储器,其地址由一个新的地址空间——虚地址(逻辑地址)定义。

逻辑地址:大家都知道,我们所接触的地址大多都从0开始,这边是逻辑地址,而真正的物理地址,是在程序被装入内存之前,由特定机构,将逻辑地址转换成物理地址。

- 缓存实际上是由内容来查找的,即使有所谓的缓存地址,那也只是一个缓存块的编号(块号)。

- 为什么要整这么多种类?

主存储器

一、概述

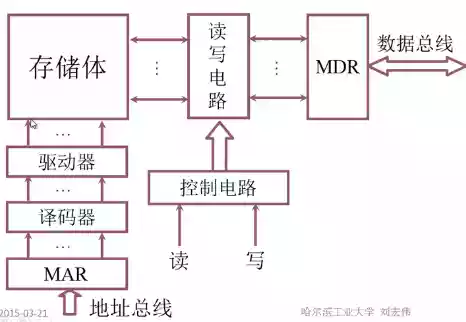

- 主存储器的基本组成

CPU和贮存的联系

- 连接信号分成三类

数据总线:完成cpu和主存间的数据传输,直接连接在MDR上,双向的,可读可写

地址总线:连接在MAR和主存间,单向传输,从CPU送到主存

控制总线:读写,单向的。

- 连接信号分成三类

主存中存储单元的地址分配

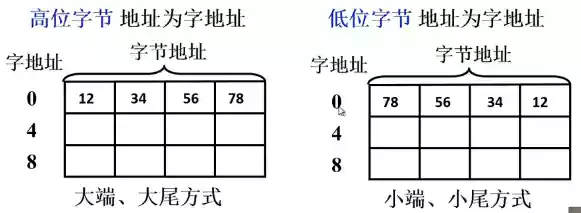

- 大端(大尾)法:高位字节存放在低地址,低位字节存在高地址,以高位地址作为高地址。

- 小端(小尾法):低位字节存放在低地址,高位字节存放在高地址,以低位字节地址为字地址

主存的技术指标

(1) 存储容量:主存存放二进制代码的总位数

(2) 存储速度:- 存取时间:存储器的访问时间,分为读出时间和写入时间

- 存取周期:连续两次独立存储器操作(读/写)所需要的最小时间间隔分为读周期和写周期

存取时间一般短于存取周期 - 存储器的带宽 位/秒

二、半导体芯片

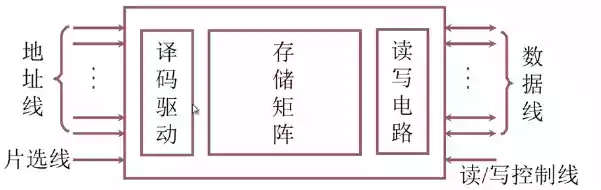

- 基本结构:

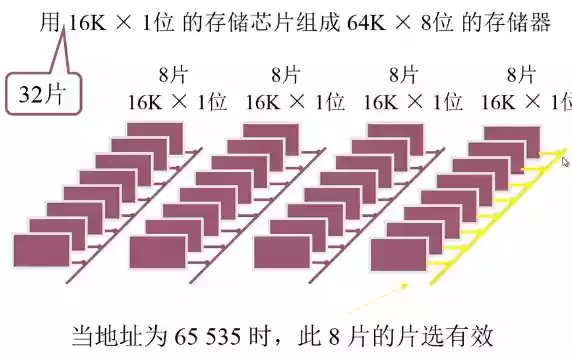

| 地址线(单向) | 数据线(双向) | 芯片容量 |

|---|---|---|

| 10 | 4 | 1K*4 |

| 14 | 1 | 16K*1 |

| 13 | 8 | 8K*8 |

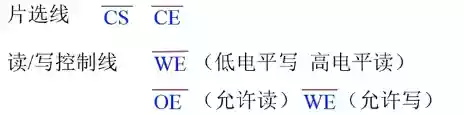

片选线:CS、CE

读/写控制线: WE(低电平写,高电平读)

OE(允许读) WE(允许写)

- 片选线的作用:让某些芯片同时工作

译码驱动方式

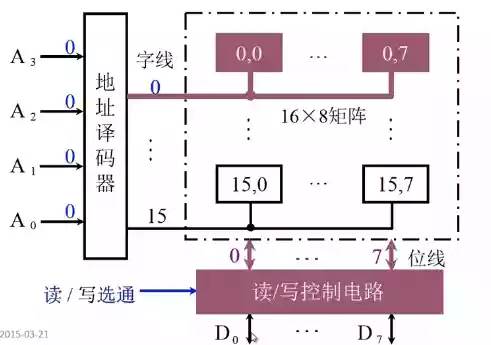

(1) 候选法

- 原理:地址译码器输入端输入4条线,输出15条字线,控制后面的15片存储器,读写控制电路有8条位线,将多片存储器并联读/写数据。当$A_0$——$A_3$输入4位的信号时,地址译码器将15条输出线中的其中一条置为高电平,表示这根线上的存储器片有效。

- 缺点:引出的地址线太多,如一个1M*8的存储器,地址译码器会输出出1M根线。

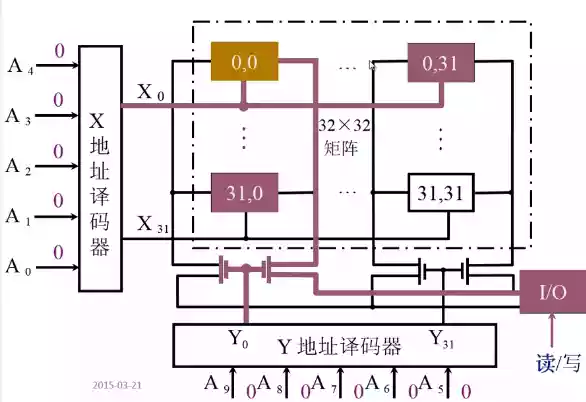

(2) 重合法:把所有存储单元布局成二维阵列。

- 原理:在重合法中,读/写数据线只有一位,每一个存储单元的位数也只有一位,当X地址(行地址)给出00000,Y地址(列地址)给出00000。则此时$X_0$输出高电平,存储单元0,0和0,31被激活(被选中),而列地址这边,$Y_0$输出高电平,$Y_0$所连接的开关被打开允许数据通过,至此,0,0可以被读写。

- 优势:当我们使用重合法控制1M*8的存储器时,我们将它们列成二维矩阵,将20位地址分成两部分,每一部分都是10位,则行地址译码器和列地址译码器输出的线都是1K条,合计2K条

三、随机存取存储器(RAM)

静态RAM(SRAM)

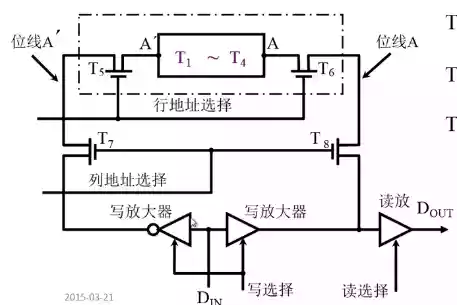

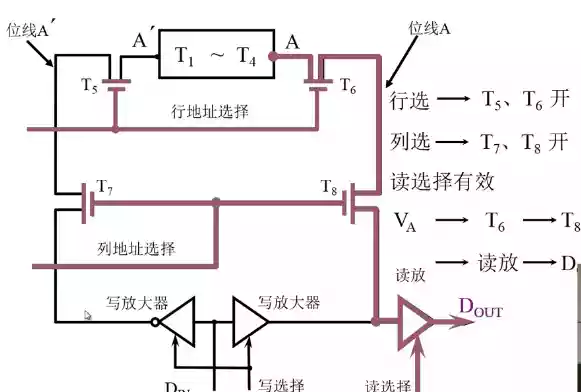

静态RAM基本电路

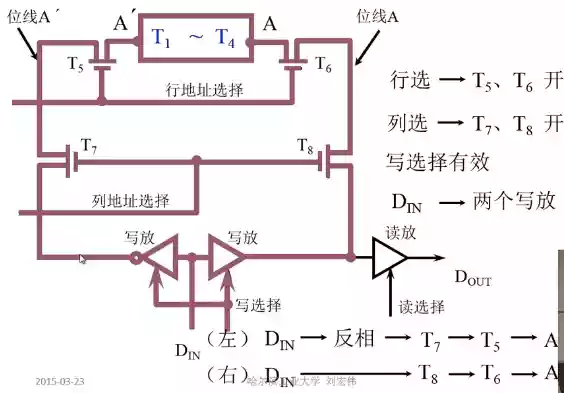

其中:

$T_1$ ~ $T_4$ 触发器(存储数据)

$T_5$、$T_6$ 行开关(一行共用)

$T_7$、$T_8$ 列开关(一列共用)

A 触发器源端(正常数据)

$A'$ 触发器非端(相当于数据取反的结果)- 读操作

- 写操作

- 读操作

静态RAM芯片举例

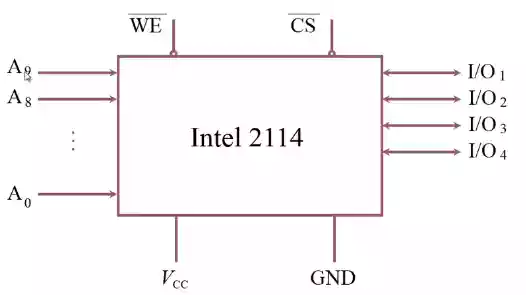

- Intel 2114 外特性

- 因此2114有1K*4个基本单元电路,选用之前所提到的重合法进行译码驱动,但是当时的例子中,一个地址只包含了一位数据(nK*1),因此在2114还需要进行改进使得一位地址可以包含四位数据(nK*4)。

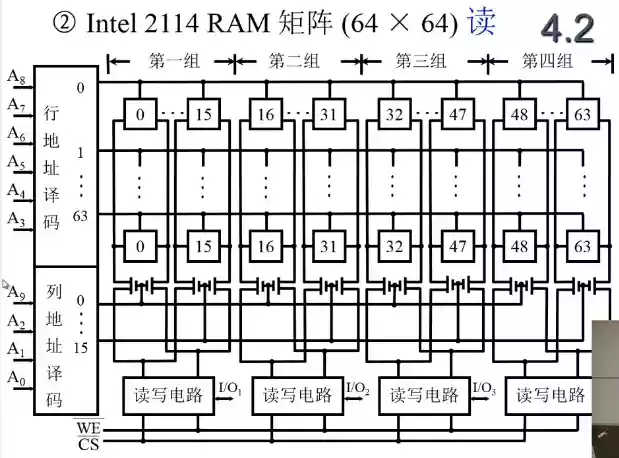

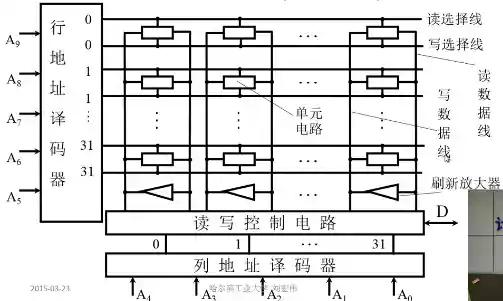

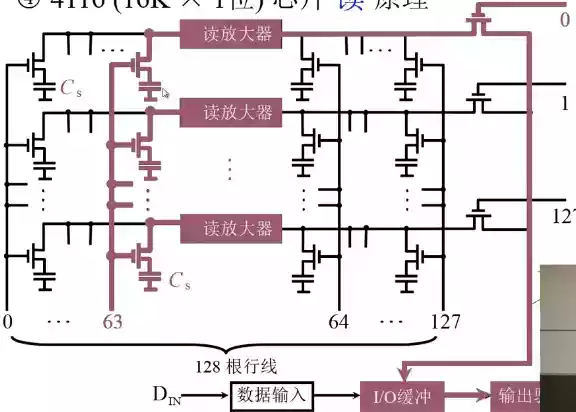

Intel 2114 矩阵(64*64) 读

4K个存储单元可以按照重合法被组合成(64*64)的矩阵。如下图所示,我们可以将64列每16列一组分成4组。64行保持不变。因此改进后的矩阵结构应该是:*行地址保持不变,有6位行地址,经过译码之后可以产生64种行选信号,而行地址只有4位,经过译码之后产生16中列选信号,因此给出一个列地址,有四行被同时选中。

Intel 2114 矩阵(64*64) 写操作与之类似

- 读写操作动态演示:

读:

写:

- Intel 2114 外特性

动态RAM(DRAM)

- 动态RAM基本单元电路:

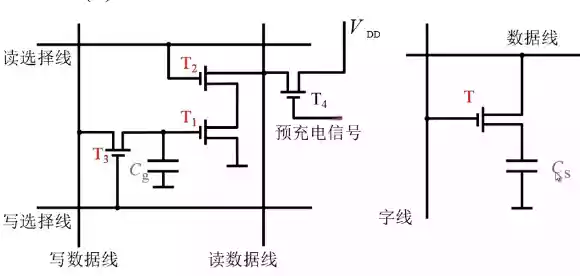

动态RAM主要分为两种,分别是三管式(左)和单管式(右) - 三管式原理:

T1,T2,T3为控制管,数据通过它们进行读写,当读选择线有效时,T2会被导通;写选择线有效,T3会导通,外部数据可以通过T3对电容器进行读写。(单管式原理与三管式相似) 三管式工作原理:

- T4是预充电管,当预充电信号有效时,T4会被打开,Vdd会经由T4对读数据线充电。

- 如果我们选择读出的话,读选择线有效,T2导通。假如此时$C_g$中保存的信息是0,此时读数据线依然保持高电平(1)。假如此时$C_g$中保存的信息是1,此时T1被导通,此时读数据线被接地,因此读数据线中的数据为0(低电平)

由此可见 :读出与原信息相反,写入与原信息相同

动态RAM芯片举例

- 三管动态RAM芯片(Intel 1103) 读

1103的地址线有10根,每次读出写入只有1K的数据,说明其存储容量为1K*1。并且每行地址译码以后每一行都对应了两根控制线,分别是读选择线和写选择线。由此可见在行地址译码的过程中,参与译码的不只是行选信号,还有读写信号。

刷新放大器:Intel 1103三管动态RAM中,每列都有一个刷新放大器用来形成再生信息。

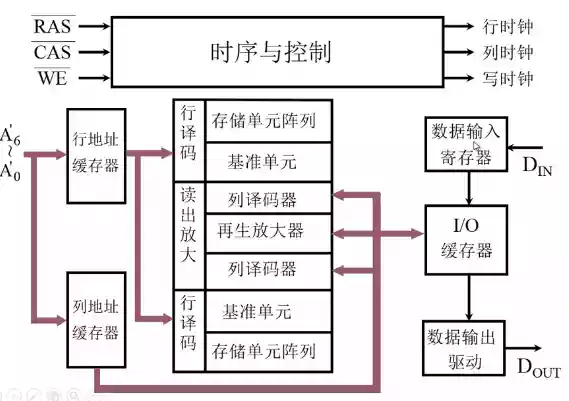

- 单管动态RAM 4116(16K*1) 外特性:

正常16K容量的存储器需要14根地址线,但是4116只有7根,这就涉及到地址线的复用,14位地址通过两次传输进存储器中,首先接收到的是7位的行地址,地址放入行地址缓冲器中,在接收7位的列地址到列地址缓冲器再进行译码。

4116还有一个自己的小控制器,由行选通信号(RAS),列选通信号(CAS),读写控制信号(WE)。产生三类时钟信号(行/列时钟,写时钟)- 4116读原理:

- 读放大器:跷跷板电路(类似于非门),因此存储器中储存的数据是真实数据取反的结果(疑问:这样做有什么作用?)

- 单管动态RAM 4116(16K*1) 外特性:

- 三管动态RAM芯片(Intel 1103) 读

动态RAM刷新:刷新只和行地址有关

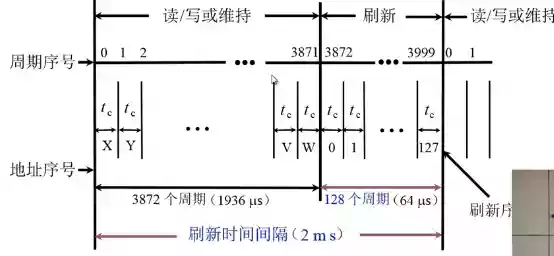

- 集中式刷新(存取周期为0.5μs):将刷新的时间,集中在一个相对集中的时间段中操作。(以128*128矩阵为例)

首先我们都知道,动态RAM的刷新时间间隔大概为2ms,因此集中刷新将2ms分成两部分,前3872个周期(1936μs)用于cup/io对于存储器的读写操作,后128周期(64μs)用于存储器芯片自身的刷新,无论cup或io都无法同存储器进行数据交换,又称之为死区(0.5μs * 128 = 64μs)。死时间率为:128/4000*100% = 3.2%.分散刷新:(存取周期为0.5μs)

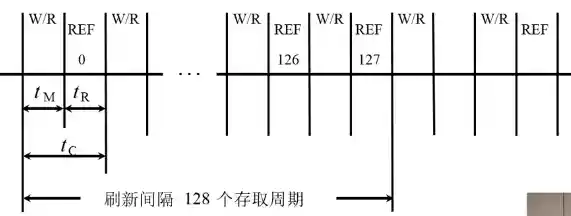

$t_M$为正常的cup/io操作周期,$t_R$为刷新的周期

$t_C$ = $t_M$ + $t_R$

刷新间隔128个刷新间隔,会造成过度刷新。- 异步刷新(分散和集中相结合):每隔15.6μs刷新一行。对于每15.6μs来说,是集中刷新,对于整个时间来说,属于分散刷新。死区为0.5*128 = 64μs,并且如果将刷新安排在指令编译状态,就不会出现死区。

- 动态RAM基本单元电路:

- 动态RAM和静态RAM的比较:

| DPAM | SRAM | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少(因为复用) | 多(不复用) |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

零散知识点

- 主存可由RAM和ROM组成